# Supercomputación basada en la arquitectura ARM

Sergio Andrés Agudelo Molina

Escuela de Ingeniería de Sistemas e Informática

Universidad Industrial de Santander

Bucaramanga, Santander

Email: sergio.agudelo@correo.uis.edu.co

Viviana Andrea Maldonado Beltrán

Escuela de Ingeniería de Sistemas e Informática

Universidad Industrial de Santander

Bucaramanga, Santander

Email: viviana.maldonado@correo.uis.edu.co

Abstract—ARM is a RISC based architecture that allows processors to require a smaller number of transistors reducing costs, heat and power. The ARM-based K supercomputer, created by Fujitsu, is among the top 10 supercomputers in the world. By 2020, its successor, the post-K computer, will be ready to become an essential tool for problem solving in the areas of bioscience, disaster prevention, environmental issues and energy.

Index Terms—Cisc, risc, ARM, x86, K computer, post-K computer, Tofu interconnect, supercomputer.

Resumen — ARM es una arquitectura basada en RISC que permite que los procesadores necesiten una cantidad menor de transistores reduciendo costes, calor y energía. La supercomputadora K creada por la compañía Fujitsu, se encuentra entre las 10 mejores supercomputadoras a nivel mundial. Para el año 2020 estará lista su sucesora, la computadora post-K y se convertirá en una herramienta esencial para la resolución de problemas en las áreas de la biociencia, la prevención de desastres, las cuestiones ambientales y la energía.

Palabras Clave — Cisc, risc, ARM, x86, computadora K, computadora post-K, interconexión Tofu, supercomputadora.

## I. INTRODUCCIÓN

Las ciencias de computación tanto de software como de hardware han evolucionado a pasos agigantados desde sus comienzos, de tal forma que prácticamente todo campo de investigación y trabajo actualmente cuenta con herramientas de este tipo que les permite trabajar de forma más eficiente y precisa. El factor más importante que representa a una computadora es su capacidad de cálculo completamente inalcanzable para el hombre lo cual nos permite alcanzar mejores resultados en menos tiempo.

En este artículo de investigación se enfoca en la descripción de la computación y supercomputación tomando temas como RISC y CISC y sus diferencias, ARM que está basada en arquitectura RISC y su diseño, supercomputación K y supercomputación post-K. La supercomputadora K fue desarrollada en alianza con la empresa tecnológica Fujitsu junto al instituto de investigación de ciencias RIKEN ubicada en la ciudad de Kobe, Japón.

Fujitsu ha estado desarrollando y suministrando supercomputadoras avanzadas por más de 30 años. Como parte de este esfuerzo, ha estado desarrollando su propio hardware incluyendo procesadores originales y software también y aumentando su experiencia técnica en supercomputadoras a lo largo del camino. Esta experiencia técnica ha sido aplicada al desarrollo de un sistema informático masivamente paralelo, la computadora K, que ahora es una de las supercomputadoras de mayor rendimiento en el mundo. La computadora K fue desarrollada como parte de la iniciativa HPCI (High Performance Computing Infrastructure) supervisada por el Ministerio de Educación, Cultura, Deportes, Ciencia y Tecnología de Japón.

Uno de los objetivos de este proyecto era lograr un rendimiento informático de 1016 operaciones de punto flotante por segundo (10 PFLOPS). Esta computadora se desarrolló no sólo para lograr el máximo rendimiento en las pruebas de referencia, sino también para garantizar un alto rendimiento efectivo en las aplicaciones utilizadas en la investigación real. Se espera para el 2020 que la supercomputadora Post-K, sucesora de la computadora K, esté en funcionamiento con una mayor escalabilidad y alto rendimiento, heredando los puntos fuertes de la computadora K.

#### II. RISC Y CISC

Una de las primeras decisiones a la hora de diseñar un microprocesador es decidir cuál será su juego de instrucciones.

La decisión por dos razones; primero, el juego de instrucciones decide el diseño físico del conjunto; segundo, cualquier operación que deba ejecutarse en el microprocesador deberá poder ser descrita en términos de un lenguaje de estas instrucciones.

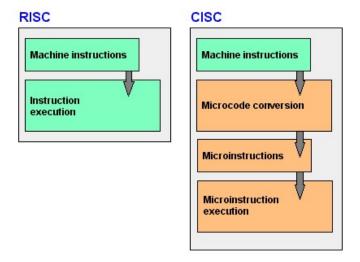

Frente a esta cuestión caben dos filosofías de diseño; máquinas denominadas CISC y máquinas denominadas RISC (Fig. 1).

Cuando hablamos de microprocesadores CISC, computadoras con un conjunto de instrucciones complejo, (del inglés complex instruction set computer), y procesadores RISC, computadoras con un conjunto de instrucciones reducido, (del inglés reduced instruction set computer), se

Fig. 1. RISC Vs. CISC

piensa que los atributos complejo y reducido describen las diferencias entre los dos modelos de arquitectura para microprocesadores.

Esto es cierto solo de forma superficial, pues se requiere de muchas otras características esenciales para definir los RISC y los CISC.

Hasta hace solo algunos años, la división era tajante: RISC se utilizaba para entornos de red, mientras que CISC se aplicaba en ordenadores domésticos. Pero en la actualidad se alzan voces que afirman que CISC está agotando sus posibilidades, mientras otras defienden fervientemente que CISC ya ha alcanzado a RISC, adoptando algunas de sus principales características.

# A. DIFERENCIAS

Las siglas CISC se refieren a computadoras con un conjunto de instrucciones complejo. Mientras RISC se refiere a computadoras con un conjunto de instrucciones reducido.

La arquitectura RISC es muchos más sencilla en comparación a la CISC requiriendo uno o pocos ciclos de ejecución, lo cual vuelve muchos más eficiente el desempeño de los RISC con el diseño de software apropiado, resultando mayor velocidad.

La arquitectura CISC habla de los microprocesadores tradicionales que operan con mayor cantidad de instrucciones en lenguaje máquina, estos procesadores tienen un conjunto de instrucciones complejas por naturaleza que requieren muchos ciclos para completar tareas.

Los RISC son menos costosos normalmente de construir y vender ya que requieren menos componentes y transistores.

| CISC                                             | RISC                                      |

|--------------------------------------------------|-------------------------------------------|

| Emphasis on hardware                             | Emphasis on software                      |

| Multiple instruction sizes and formats           | Instructions of same set with few formats |

| Less registers                                   | Uses more registers                       |

| More addressing modes                            | Fewer addressing modes                    |

| Extensive use of microprogramming                | Complexity in compiler                    |

| Instructions take a varying amount of cycle time | Instructions take one cycle time          |

| Pipelining is difficult                          | Pipelining is easy                        |

## B. ARQUITECTURA CISC

En arquitectura computacional, CISC (del inglés Complex Instruction Set Computer, en español Computador con Conjunto de Instrucciones Complejas) es un modelo de arquitectura de computadores. Los microprocesadores CISC tienen un conjunto de instrucciones que se caracteriza por ser muy amplio y permitir operaciones complejas entre operandos situados en la memoria o en los registros internos, en contraposición a la arquitectura RISC.

## C. ARQUITECTURA RISC

En arquitectura computacional, RISC (del inglés Reduced Instruction Set Computer, en español Computador con Conjunto de Instrucciones Reducidas) es un tipo de diseño de CPU generalmente utilizado en microprocesadores o microcontroladores con las siguientes características fundamentales:

- 1. Instrucciones de tamaño fijo y presentado en un reducido número de formatos.

- 2. Sólo las instrucciones de carga y almacenamiento acceden a la memoria de datos.

Además estos procesadores suelen disponer de muchos registros de propósito general. El objetivo de diseñar máquinas con esta arquitectura es posibilitar la segmentación y el paralelismo en la ejecución de instrucciones y reducir los accesos a memoria. Las máquinas RISC protagonizan la tendencia actual de construcción de microprocesadores. PowerPC, DEC Alpha, MIPS, ARM, SPARC son ejemplos de algunos de ellos.

RISC es una filosofía de diseño de CPU para computadora que está a favor de conjuntos de instrucciones pequeñas y simples que toman menor

#### tiempo para ejecutarse.

El tipo de procesador más comúnmente utilizado en equipos de escritorio, el x86, está basado en CISC en lugar de RISC, aunque las versiones más nuevas traducen instrucciones basadas en CISC x86 a instrucciones más simples basadas en RISC para uso interno antes de su ejecución.

La idea fue inspirada por el hecho de que muchas de las características que eran incluidas en los diseños tradicionales de CPU para aumentar la velocidad estaban siendo ignoradas por los programas que eran ejecutados en ellas. Además, la velocidad del procesador en relación con la memoria de la computadoraque accedía era cada vez más alta. Esto conllevó la aparición de numerosas técnicas para reducir el procesamiento dentro del CPU, así como de reducir el número total de accesos a memoria. Terminología más moderna se refiere a esos diseños como **arquitecturas de carga-almacenamiento.**

#### Multitarea

Debido a lo redundante de las microinstrucciones, los sistemas operativos diseñados para estos microprocesadores, contemplaban la capacidad de subdividir un microprocesador en varios, reduciendo el número de instrucciones redundantes por cada instancia del mismo. Con una arquitectura del software optimizada, los entornos visuales desarrollados para estas plataformas, contemplaban la posibilidad de ejecutar varias tareas en un mismo ciclo de reloj. Así mismo, la paginación de la memoria RAM era dinámica y se asignaba una cantidad suficiente a cada instancia, existiendo una especie de 'simbiosis' entre la potencia del microprocesador y la RAM dedicada a cada instancia del mismo.

## III. ARM

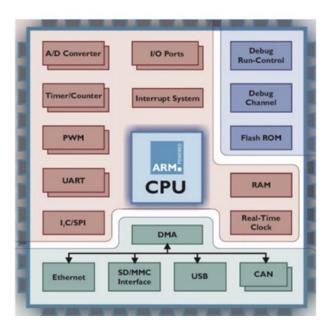

Posterior a RISC y CISC vienen diversas familias ARM, como las que se muestran en la Fig. 2.

ARM es una arquitectura basada en RISC (Reduced Instruction Set Computer=Ordenador con Conjunto Reducido de Instrucciones) de 32 bits y, recientemente, con la llegada de su versión V8-A, también de 64 Bits, desarrollada por ARM Holdings. Se llamó Advanced RISC Machine, y anteriormente Acorn RISC Machine. La arquitectura ARM es el conjunto de instrucciones de 32 y 64 bits más ampliamente utilizado en unidades producidas. Concebida originalmente por Acorn Computers para su uso en ordenadores personales, los primeros productos basados en ARM eran los Acorn Archimedes, lanzados en 1987. Tiene un enfoque de uso reducido de transistores garantizando alto rendimiento y alta eficiencia energética.

Un enfoque de diseño basado en RISC permite que los procesadores ARM necesitan una cantidad menor de transistores que los procesadores x86 CISC, típicos en la mayoría de ordenadores personales. Este enfoque de diseño nos lleva, por tanto, a una reducción de los costes, calor y energía. Estas

| Arquitectura | Familia                    |

|--------------|----------------------------|

| ARMv1        | ARM1                       |

| ARMv2        | ARM2, ARM3                 |

| ARMv3        | ARM6, ARM7                 |

| ARMv4        | StrongARM, ARM7TDMI        |

| ARMv5        | ARM7EJ, ARM9E,XScale       |

| ARMv6        | ARM11, ARM Cortex-M        |

| ARMv7        | ARM Cortex-A, ARM Cortex-R |

| ARMv8        | ARM Cortex-A50             |

Fig. 2. Familias ARM

características son deseables para dispositivos que funcionan con baterías, como los teléfonos móviles, tabletas, etc.

La relativa simplicidad de los procesadores ARM los hace ideales para aplicaciones de baja potencia. Como resultado, se han convertido en los dominantes dentro del mercado de la electrónica móvil e integrada, encarnados en microprocesadores y microcontroladores pequeños, de bajo consumo y relativamente bajo costo. En 2005, alrededor del 98% de los más de mil millones de teléfonos móviles vendidos utilizaban al menos un procesador ARM. Desde 2009, los procesadores ARM son aproximadamente el 90% de todos los procesadores RISC de 32 bits integrados. Cabe hacer mención que no existe una tabla de equivalencias de rendimiento entre las distintas tecnologías de procesadores4 que se utilizan generalmente en la electrónica de consumo, incluyendo PDA, tabletas, teléfonos móviles, teléfonos inteligentes, relojes inteligentes,

videoconsolas portátiles, calculadoras, reproductores digitales multimedia (fotos, vídeos, etc.) y periféricos de ordenador como discos duros y enrutadores.

Fig. 3. Procesador ARM en una impresora HP

La arquitectura ARM es licenciable. Esto significa que el negocio principal de ARM Holdings es la venta de núcleos IP, estas licencias se utilizan para crear microcontroladores y CPUs basados en este núcleo (Fig. 4).

Fig. 4. Diagrama de un micro con arquitectura ARM.

El diseño del ARM se ha convertido en uno de los más usados del mundo, desde discos duros hasta juguetes. Hoy en día, cerca del 75% de los procesadores de 32 bits poseen este chip en su núcleo.

#### Diseño

El juego de instrucciones del ARM es similar al del MOS

6502, pero incluye características adicionales que le permiten conseguir un mejor rendimiento en su ejecución. Para mantener el concepto tradicional de RISC, se estableció la ejecución de una orden en un tiempo, por lo general, de un ciclo. La característica más interesante es el uso de los 4 bits superiores como código de condición, haciendo que cualquier instrucción pueda ser condicional. Este corte reduce el espacio para algunos desplazamientos en el acceso a la memoria, pero permite evitar perder ciclos de reloj en el pipeline al ejecutar pequeños trozos de código con ejecución condicional.

El ejemplo típico es el Máximo común divisor, según el algoritmo de Euclides.

# Ejemplo en C:

```

int gcd(int i, int j)

{

while (i != j)

if (i > j)

i -= j;

else

j -= i;

return i;

}

```

Fig. 5. Código en C.

Expresado en código ensamblador ARM, el ciclo, incluyendo una rotación de operandos, puede expresarse del siguiente modo (Fig. 6):

```

b test

loop subgt Ri, Ri, Rj

suble Rj, Rj, Ri

test cmp Ri, Rj

bne loop

```

Fig. 6.

## Sistemas operativos

Diversos sistemas operativos han implementado la arquitectura ARM tales como: Acorn systems, Sistemas operativos integrados, UNIX, Tipo UNIX, Linux, BSD, Windows, etc.

#### IV. SUPERCOMPUTADORAS

## A. DEFINICIÓN

Una supercomputadora es aquella con capacidades de cálculo muy superiores a las computadoras comunes y de escritorio y que son usadas con fines específicos. También se le conoce como computadora de alto rendimiento y ambiente de cómputo de alto rendimiento, ya que las supercomputadoras son un conjunto de poderosos ordenadores unidos entre sí para aumentar su potencia de trabajo y rendimiento [8].

## B. ACTUALIDAD

De acuerdo al proyecto *Top500* [9], que es el ranking de las 500 supercomputadoras con mayor rendimiento del mundo, en su 49<sup>a</sup> edición (Junio de 2017), se presentan a continuación los 10 primeros puestos de supercomputadoras:

**Sunway TaihuLight**, un sistema desarrollado por el Centro Nacional de Investigación de Ingeniería y Tecnología de Computadores Paralelos de China (NRCPC) e instalado en el Centro Nacional de Supercomputación de Wuxi. Con un rendimiento Linpack de 93 petaflops, TaihuLight ocupa el primer puesto (Fig. 7).

Fig. 7. Sunway TaihuLight: Centro Nacional de Supercomputación en Wuxi No.1 desde Jun 2016 hasta Jun 2017

**Tianhe-2**, un sistema desarrollado por la Universidad Nacional de Tecnología de Defensa de China (NUDT) y desplegado en el Centro Nacional de Supercomputadoras de Guangzho, China, ocupa el segundo lugar con una marca Linpack de 33,9 petaflops. Fue el sistema número uno en la lista TOP500 durante tres años consecutivos, hasta que TaihuLight lo superó en junio de 2016 (Fig. 8).

Fig. 8. Tianhe-2 (MilkyWay-2): Universidad Nacional de Tecnología de Defensa No.1 de Jun 2013 hasta Nov 2015

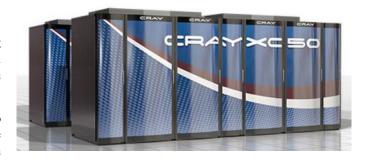

**Piz Daint** última versión, con un sistema Cray XC50 instalado en el Centro Nacional Suizo de Supercomputación (CSCS) es el número tres. La actualización se realizó con GPUs NVIDIA Tesla P100 adicionales, duplicando el rendimiento de Linpack de la marca anterior del sistema de 9,8 petaflops en noviembre de 2016, que fue el resultado de una actualización significativa. El actual resultado de Piz Daint de 19,6 petaflops permitió al sistema subir cinco posiciones en el ranking (Fig. 9).

Fig. 9. Piz Daint: Centro Nacional Suizo de Supercomputación

**Titan**, un sistema Cray XK7 instalado en el Departamento de Energía (DOE) Oak Ridge National Laboratory, es el número cuatro en el ranking. Su marca Linpack de 17,6 petaflops se ha mantenido constante desde su instalación en 2012 (Fig. 10).

Fig. 10. Titan: Oak Ridge National Laboratory No.1 en Noviembre de 2012

Completan los 10 primeros:

- **Sequoia** (17,2 petaflops), un sistema IBM BlueGene / Q instalado en el Laboratorio Nacional Lawrence Livermore del DOE, ocupa el lugar número cinco (Fig. 11).

- Cori (14.0 petaflops), un sistema Cray XC40 alojado en el Centro Nacional de Investigación Científica en Ciencias de la Energía (NERSC), es el número seis (Fig. 12).

- Oakforest-PACS (13,6 petaflops), un sistema Fujitsu PRIMERGY que funciona en el Japan's Joint Center for Advanced High Performance Computing, es el número siete. (Fig. 13).

- La computadora K de Fujitsu (10,5 petaflops), instalada en el Instituto Avanzado de Ciencias Computacionales

Fig. 11. Sequoia: Laboratorio Nacional Lawrence Livermore No. 1 en Junio de 2012

Fig. 12. Cori: National Energy Research Scientific Computing Center

RIKEN (AICS), ocupa el puesto número ocho (Fig. 14).

- **Mira** (8,6 petaflops), un sistema IBM BlueGene/Q instalado en el Laboratorio Nacional Argonne de DOE, es el número nueve (Fig. 15).

- **Trinity** (8.1 petaflops), un sistema Cray XC40 que funciona en Los Alamos National Laboratory, es el número diez (Fig. 16).

## V. COMPUTADORA K

La computadora K, que tenía el título de la supercomputadora más rápida del mundo desde junio de 2011 hasta junio de 2012, ocupa ahora el octavo puesto. El superordenador tiene una capacidad de 10.51 petaflops (10,510 billones de operaciones por segundo). De ahí el nombre de la computadora: La letra "K" es la abreviatura de la palabra japonesa "kei", que significa 10,000 billones.

La computadora K sólo tiene CPU, no cuenta con aceleradores GPU. Eso hace que sea un superordenador verdaderamente masivo: físicamente tiene 864 racks de computadoras (estantes o gabinetes), cuatro veces el número de gabinetes del sistema Titán.

Fig. 13. Oakforest-PACS: Japan's Joint Center for Advanced High Performance Computing

Fig. 14. Computadora K: Instituto Superior de Ciencias Computacionales RIKEN No.1 desde Junio de 2011 hasta Nov 2011

K es utilizada en el Instituto Riken de Investigación Física y Química en Kobe, Japón. El Instituto Riken comparte su poder informático con otros proyectos científicos de todo el mundo [10].

El equipo K se basa en una arquitectura de memoria distribuida con más de 80.000 nodos de computadora. Se utiliza para una variedad de aplicaciones, incluyendo investigación climática, prevención de desastres e investigación médica. El sistema operativo de la computadora K se basa en el kernel de Linux, con controladores adicionales diseñados para hacer uso del hardware de la computadora.

En junio de 2011, TOP500 clasificó a K el superordenador más rápido del mundo, con una velocidad de cómputo de más de 8 petaflops, y en noviembre de 2011, K se convirtió en la primera computadora en alcanzar los 10 petaflops.

En un principio se había programado para completarse en junio de 2012. En junio de 2012, K fue sustituido por la American IBM Sequoia. A partir de junio de 2017, K es la octava computadora más rápida del mundo, con los chinos Sunway TaihuLight y Tianhe-2 siendo los supercomputadores más rápidos [11].

Fig. 15. Mira: Laboratorio Nacional Argonne de DOE

Fig. 16. Trinity: Los Alamos National Laboratory

# A. RENDIMIENTO

El 20 de junio de 2011, K había establecido un registro LINPACK con una actuación de 8,162 petaflops, lo que la convirtió en la supercomputadora más rápida del mundo en ese momento; logró este rendimiento con un índice de eficiencia informática de 93,0%. El récord anterior lo tenía Tianhe - 1A en la National University of Defense Technology con 2,507 petaflops. En noviembre de 2011, Riken informó que K se había convertido en el primer superordenador en superar los 10 petaflops, logrando un desempeño de LINPACK de 10,51 cuatrillones de cálculos por segundo, con un índice de eficiencia informática de 93.2%. K recibió el primer lugar en los cuatro puntos de referencia de rendimiento en el 2011 HPC Challenge Awards.

El 18 de junio de 2012, el Comité del Proyecto TOP500 anunció que el superordenador IBM Sequoia en California había reemplazado a K como el superordenador más rápido del mundo, con un rendimiento LINPACK de 16,325 petaflops. Sequoia es 55% más rápido que K, utilizando 123% más procesadores de CPU, pero también es un 150% más eficiente en energía. A partir de junio de 2013, el superordenador más rápido del mundo fue el Tianhe-2, capaz de un rendimiento de LINPACK de más de 33 petaflops.

En la lista TOP500, se hizo primero en junio de 2011, cayendo a través del tiempo a posiciones más bajas, séptimo en noviembre de 2016 y octavo en junio de 2017 (Fig. 17).

El 16 de noviembre de 2016, la computadora K tomó el primer lugar en el HPCG Benchmark, propuesta por Jack Dongarra, un nuevo índice desarrollado para crear una visión más realista del rendimiento del supercomputador en comparación con el punto de referencia LINPACK de uso común. Para esta competición, se utilizaron todos los 82.944 nodos de computación de K, logrando un rendimiento de 602 teraflops, una puntuación bastante superior a los 461 teraflops que alcanzó al tomar el segundo lugar en 2014 [12].

El 19 de junio de 2017, la computadora K tomó el primer lugar por segunda vez consecutiva en el HPCG Benchmark. Para este resultado [13], se usó la misma cantidad de nodos del año anterior, logrando un rendimiento de 602 teraflops nuevamente. Esta cifra es superior a la de los supercomputadores que quedaron más altos que la computadora K en las clasificaciones TOP500, lo que demuestra un desempeño sobresaliente en varios campos de la ciencia y la ingeniería.

#### B. ESPECIFICACIONES

• Configuración del nodo de cálculo: Un nodo de cálculo consta de una CPU, memoria y una interconexión.

## 1) *CPU*:

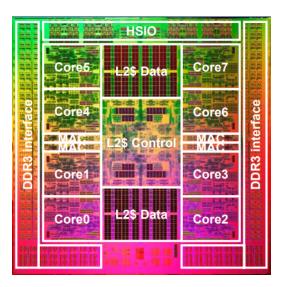

La computadora K posee 88.128 procesadores SPARC64 VIIIfx con 8 núcleos por procesador, que son "las unidades mínimas que realizan cálculos" y 2,0 GHz, es decir, un total de 705.024 núcleos (Fig. 18). Se encuentran instalados en 672 compartimentos, y se espera una ampliación a 800 compartimentos, lo que elevaría su poder de cálculo.

SPARC64 VIIIfx cuenta con la avanzada tecnología de procesamiento de semiconductores de 45 nm de Fujitsu y una eficiencia energética de 2,2 GFLOPS/W lograda mediante la implementación de medidas de reducción de potencia tanto desde el punto de vista de la tecnología de proceso como del diseño [14]. Esta CPU tiene una caché L2 de 6 megabytes compartida por estos núcleos.

Un nodo de cálculo consta de un solo chip de CPU. Su máximo rendimiento es de 128 giga-flops. Como resultado de estas características, el SPARC64 VIIIfx logra un alto rendimiento de ejecución en el campo HPC.

El calor generado por las CPU's durante el funcionamiento es gestionado por un sistema de refrigeración por agua para reducir la tasa de fallos de la CPU.

| CLASIFIC | CACIÓN |                                                        |          |                  |                  |                   |                  |

|----------|--------|--------------------------------------------------------|----------|------------------|------------------|-------------------|------------------|

| Lista    | Rango  | Sistema                                                | Vendedor | Cores<br>Totales | Rmax<br>(TFlops) | Rpeak<br>(TFlops) | Potencia<br>(kW) |

| 06/2017  | 8      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 11/2016  | 7      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 06/2016  | 5      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 11/2015  | 4      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 06/2015  | 4      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 11/2014  | 4      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 06/2014  | 4      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 11/2013  | 4      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 06/2013  | 4      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 11/2012  | 3      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 06/2012  | 2      | K ordenador, SPARC64 VIIIfx 2.0GHz, interconexión Tofu | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

| 11/2011  | 1      | K ordenador, SPARC64 VIIIfx 2.0GHz,                    | Fujitsu  | 705.024          | 10.510,0         | 11.280,4          | 12.659,89        |

Fig. 17. Ranking Computadora K

Fuiitsu

interconexión Tofu

interconexión Tofu

K ordenador, SPARC64 VIIIfx 2.0GHz,

06/2011 1

Fig. 18. SPARC64 VIIIfx

# 2) MEMORIA:

DDR3-SDRAM-DIMM se utiliza como memoria principal. El módulo de memoria con contactos

duales (DIMM) es un módulo de productos que también se utiliza en servidores y clústeres de PC, lo que proporciona una serie de ventajas. Por ejemplo, puede ser de múltiples fuentes, se puede obtener un suministro estable de unos 700000 módulos en un período de fabricación de aproximadamente un año con un nivel de calidad estable, y se pueden seleccionar módulos con especificaciones de consumo de energía superiores.

Además de esto, una interfaz de memoria de 8 canales por CPU proporciona un ancho de banda de memoria máxima de 64 GB/s, superando el de los ordenadores de los competidores y el alto rendimiento de memoria que se considera necesario para la computación científica.

## 3) INTERCONEXIÓN:

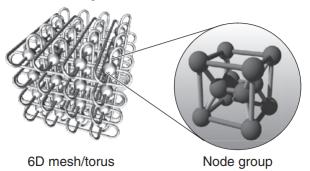

La computadora K implementa una arquitectura de interconexión denominada "Tofu" que es utilizada para computadoras masivamente paralelas y ha sido desarrollada para que interconecta más de 80000 nodos. Con una escalabilidad de más de 100000 nodos,

la interconexión Tofu (Fig. 19) constituye una red de interconexión directa que proporciona conexiones escalables con baja latencia y alto rendimiento, para un grupo masivamente paralelo de CPUs y logra alta disponibilidad y operabilidad mediante el uso de una configuración 6D mesh/torus [15].

Fig. 19. Interconexión Tofu

El diseño de la topología 6D mesh/torus en la computadora K proporciona muchas rutas de comunicación entre CPUs vecinas. La ejecución de comunicaciones de datos entre CPUs a través de la ruta más corta y durante el período más corto de tiempo se habilita para asegurar que la red pueda extraer completamente la potencia computacional de CPU de primera clase mundial. Además, esta topología está soportada por una versión optimizada con tofu de la librería open-source Open MPI Message Passing Interface.

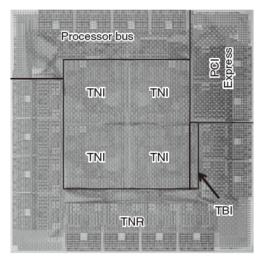

La interconexión Tofu posee enlaces full-duplex que tienen un ancho de banda máximo de 10 GB/s (5 GB/s por dirección). Cada nodo está conectado a su propio chip InterConnect Controller (ICC) (Fig. 20), que contiene cuatro interfaces Tofu (una para el nodo y tres para conectarse a otros chips ICC) y un enrutador [16].

Fig. 20. Chip ICC

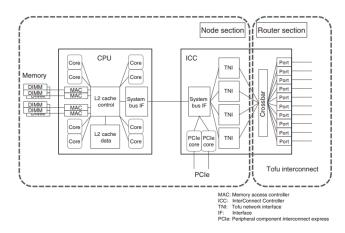

Un nodo de cálculo de la computadora K consiste en la CPU/DIMM descrita anteriormente y un chip InterConnect Controller (ICC) para implementar la interconexión. Dado que la interconexión Tofu forma una red de interconexión directa, la ICC incluye una función para retransmitir paquetes entre otros nodos (Fig. 21).

Fig. 21. Diagrama conceptual de las secciones de nodo y router.

Si la sección de nodo de un nodo de cálculo falla, sólo se afectará el trabajo que utiliza ese nodo de cálculo, pero si la sección de router de ese nodo de cálculo falla, todos los trabajos que utilizan ese nodo de cálculo como punto de retransmisión de paquetes se verán afectados. La tasa de fallos de la sección de enrutador es casi proporcional a la cantidad de circuitería que contiene, y necesita ser significativamente menor que la tasa de fallo de la sección de nodo. Por lo tanto, las fallas de chip ICC se categorizan de acuerdo con su impacto, que determina la acción tomada en el momento de una ocurrencia de falla. El resultado final es un mecanismo para continuar el funcionamiento del sistema en el caso de un fallo en una sección de nodo.

- Sistema de archivos: El sistema adopta un sistema de archivos local/global de dos niveles con funciones paralelas/distribuidas y proporciona a los usuarios una función de estadificación automática para mover archivos entre sistemas de archivos globales y locales. Fujitsu desarrolló un sistema de archivos paralelo optimizado basado en Lustre, llamado Fujifax Exabyte File System (FEFS), que es escalable a varios cientos de petabytes.

- Consumo de energía: Aunque la computadora K reportó el mayor consumo total de energía de cualquier supercomputadora TOP500 2011 (9,89 MW el equivalente a casi 10.000 hogares suburbanos), es relativamente eficiente, alcanzando 824,6 GFlop/kWatt, es decir, 29.8% más eficiente que el NUDT TH MPP

de China (clasificado #2 en 2011), y 225.8% más eficiente que el Jaguar-Cray XT5-HE de Oak Ridge (clasificado #3 en 2011). Sin embargo, la eficiencia energética de K aún está muy por debajo del récord de 2097.2 GFlops/kWatt establecido por el NNSA/SC Blue Gene/Q Prototype 2 de IBM. A modo de comparación, el consumo medio de un sistema TOP 10 en 2011 fue de 4,3 MW y la eficiencia media fue de 463,7 GFlop/kW.

Según el creador de TOP500, Jack Dongarra, profesor de ingeniería eléctrica y ciencias de la computación en la Universidad de Tennessee, el rendimiento de la computadora K es igual a "un millón de computadoras de escritorio vinculadas". Los costos anuales de funcionamiento de la computadora se estiman en 10 millones de dólares.

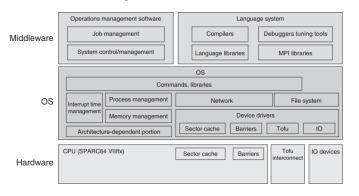

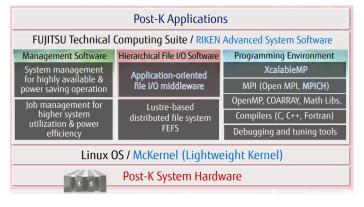

• **Sistema operativo:** El software básico de la computadora K está compuesto por el sistema operativo y el middleware básico (software de gestión de operaciones, sistema de idiomas) (Fig. 22).

Fig. 22. Configuración del Software de la computadora K

El sistema operativo implementa la parte dependiente de la arquitectura del kernel de Linux y tiene controladores adicionales para usar el hardware de la computadora K para que pueda ser utilizado desde el middleware en el nivel superior. El desarrollo del sistema operativo se muestra en la Tabla 1 [17].

|                      | Feature                                    | Realization method                                                                                                            |

|----------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Improved usability   | Effective utilization of user assets       | Linux<br>POSIX API                                                                                                            |

| Improved performance | Direct control of hardware extensions      | SIMD instruction support<br>Hardware barrier<br>Sector cache<br>Extension of device drivers for<br>hardware control registers |

|                      | Improved scalability                       | Synchronization scheduling with rsadc                                                                                         |

|                      | Improved memory performance and efficiency | Large page support                                                                                                            |

| Improved robustness  | Security<br>RAS enhancement                | User access protection<br>Fallback for failure                                                                                |

Tabla 1. Características del sistema operativo de K.

## VI. COMPUTADORA POST-K

ARM estaba llevando un perfil bajo en la batalla para destronar a x86 como la plataforma dominante para los

sistemas de computación de alto rendimiento. Ese perfil bajo cambió en la conferencia ISC 2016, donde Fujitsu anunció que desarrollaría un procesador ARM para su supercomputadora exascale Post-K. El anuncio lo hizo Toshiyuki Shimizu y como parte de su presentación, reveló que su supercomputadora exascale programada para ser completada en 2020, estará compuesta por procesadores ARM de 64 bits que serán diseñados para ejecutar aplicaciones HPC. RIKEN, el instituto de investigación científica más grande y prestigioso de Japón, será el receptor del futuro sistema. El trabajo de diseño del procesador HPC se realizará en colaboración con ARM Holdings, la empresa que desarrolla y licencia la propiedad intelectual de ARM [18].

#### A. OBJETIVOS DE POST-K

- Alto rendimiento de la aplicación y buena eficiencia energética.

- Mantener la compatibilidad de la aplicación mientras va mejorando con respecto a sus versiones anteriores.

- Buena usabilidad y mejor accesibilidad para los usuarios.

# B. ESPECIFICACIONES

La supercomputadora Post-K representa la cuarta generación de la línea de supercomputación "K" de Fujitsu, que hasta ahora estaba basada en procesadores SPARC64.

El sistema Post-K fue diseñado para ser un esfuerzo más personalizado, no sólo en el departamento de procesadores, sino también con respecto a la red del sistema, que en este caso será la interconexión Tofu de Fujitsu que será heredada de la FX10 y FX100 (Fig 23).

Fig. 23. El concepto de diseño HPC de Fujitsu para Post-K.

• CPU, núcleos e interconexión: La intención de Fujitsu es construir una arquitectura ARM adaptada a cargas de trabajo HPC, con el nivel de rendimiento de punto flotante que eso implica. Esto significa que el chip ofrecerá capacidades de procesamiento de vectores mucho más potentes que las disponibles actualmente en ARMv8, así como otras características asociadas en arquitecturas como el SPARC64.

ARMv8 destaca la verdadera fortaleza de la microarquitectura de Fujitsu (Fig. 24), ya que éste ha diseñado su propio procesador de alto rendimiento que ejecuta software ARMv8 de 64 bits en lugar de tomar un núcleo ARM para el papel. La computadora Post-K tiene una CPU de alto rendimiento basada en ARMv8 con SVE ISA para contribuir al desarrollo de SVE (Extensión vectorial escalable) con ARM.

| HPC apps acceleration                                                                              | Post-K     | FX100            | FX10            | K computer      |  |  |

|----------------------------------------------------------------------------------------------------|------------|------------------|-----------------|-----------------|--|--|

| Base ISA + SIMD Extensions                                                                         | ARMv8+SVE  | SPARCv9+HPC-ACE2 | SPARCv9+HPC-ACE | SPARCv9+HPC-ACE |  |  |

| SIMD width [bit]                                                                                   | 512        | 256              | 128             | 128             |  |  |

| Gather Load and Scatter Store                                                                      | ✓Enhanced  | V                | -               | -               |  |  |

| FMA: Floating-point multiply and add                                                               | V          | V                | ~               | ~               |  |  |

| Packed Single Precision SIMD                                                                       | ✓ Enhanced | V                | -               | -               |  |  |

| Math. acceleration primitives*                                                                     | ✓ Enhanced | ✓ Enhanced       | ~               | ~               |  |  |

| Inter-core barrier                                                                                 | V          | V                | ~               | ~               |  |  |

| Sector cache                                                                                       | ✓ Enhanced | ✓ Enhanced       | ~               | ~               |  |  |

| Hardware "prefetch" assist                                                                         | ✓ Enhanced | ✓Enhanced        | ~               | ~               |  |  |

| *Mathematical acceleration primitives include trigonometric functions, exponential functions, etc. |            |                  |                 |                 |  |  |

Fig. 24. Comparación de la computadora Post-K con otras computadoras.

Cabe destacar que los núcleos de la CPU Fujitsu son compatibles con ARM SVE ISA. Cada núcleo Fujitsu ARM incorpora la probada microarquitectura del supercomputador de Fujitsu y ellos, como socio líder en el desarrollo de ARM SVE, contribuyen a la especificación de ARM SVE (Scalable Vector Extension) para el rendimiento de la aplicación. ARM SVE, además de funciones opcionales y de una interconexión Tofu, mantienen los modelos de programación y el equilibrio de rendimiento. Por lo tanto, Post-K cumple con los marcos estándares de ARM para la compatibilidad entre plataformas usando la herencia y mejora de las funciones de las CPUs precedentes [20].

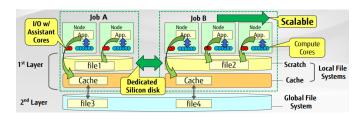

• Sistema de archivos: Post-K tiene un nuevo sistema de archivos local para acelerar el procesamiento de I/O (transferencia de datos). Además, tiene un sistema de archivos de primera capa basado en disco de silicio asignado para cada trabajo. Tiene computación simultánea y acceso a archivos mediante la descarga de I/O con núcleos auxiliares y posee un rendimiento escalable según el tamaño del trabajo (> 10000 nodos) (Fig. 25).

Fig. 25. Comparación de la computadora Post-K con otras computadoras.

## • Hardware:

- CPU con SVE.

- Interconexión Tofu 6D mesh/torus.

- Arquitectura Manycore.

- Sistema de almacenamiento jerárquico de 3 niveles:

- \* Disco de silicio.

- \* Disco magnético.

- \* Almacenamiento para archivos [21].

#### Continua con un diseño de:

- Arquitectura de nodos.

- Configuración del sistema.

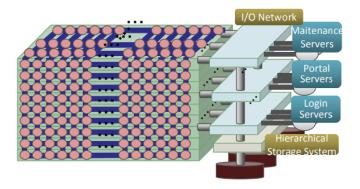

- Sistema de almacenamiento (Fig. 26).

Fig. 26. Hardware.

o **Software:** Actualmente en desarrollo, basado en un esquema de "co-diseño" con desarrolladores de aplicaciones, incluyendo hardware del sistema (Fig. 27).

#### Otras de sus características serían:

- Mantener la portabilidad de las aplicaciones proporcionando un entorno de programación.

- Diseño funcional del sistema operativo.

- Diseño funcional de la comunicación.

- Lenguaje de programación altamente productivo y bibliotecas matemáticas.

- Multi-Kernel: Linux con Lightweight Kernel.

- Interfaz de I/O de archivos para sistemas y aplicaciones de almacenamiento jerárquico de 3 niveles.

- MPI+entorno de programación OpenMP.

Fig. 27. Software de sistema avanzado para Post-K.

## VII. CONCLUSIONES

- ARM y X86 son las dos arquitecturas dominantes hoy en día puesto que presentan por su lado una gran eficiencia energética o un gran desempeño en rendimiento respectivamente.

- La mejora de las diferentes arquitecturas a través del tiempo es notable empezando primero con CISC y RISC y llegando a ARM y X86, arquitecturas con las cuales podemos ver el avance de las tecnologías de computación.

- ARM presenta como su principal característica el alto consumo de energía al contener menor cantidas de transistores, lo cual lo vuelve ideal para dispositivos que utilizan baterías.

- ARM y sus diferentes familias son los más utilizados en la actualidad en la mayoría de dispositivos Smartphone y es que esto es necesario a menos que se quiera un equipo potente pero de poca duración de batería.

- Los objetivos de desarrollo establecidos para la computadora K exigían un sistema informático de gran rendimiento a gran escala, con una importancia atribuida a la alta fiabilidad y alta disponibilidad desde la fase de diseño. RIKEN y Fujitsu han estado trabajando para lograr el pico máximo de rendimiento efectivo de aplicaciones y para construir un sistema de alta fiabilidad y alta disponibilidad. El equipo K se ubicó en el puesto Nº 1 de la lista de referencia TOP500 de junio de 2011 y descendió al puesto Nº 8 en junio de 2017. También logra 10,51 PFLOPS de rendimiento de LINPACK. Estos logros demuestran que sus objetivos se cumplieron constantemente.

- La supercomputadora Post-K basada en ARM tiene un objetivo de rendimiento de ser 100 veces más rápido que la supercomputadora K dentro de un poder que sólo será 3-4 veces el de su predecesor, esto es, debido a su CPU de alto rendimiento basadada en ARMv8 con SVE ISA.

## REFERENCIAS

- [1] "Arquitectura RISC CISC", Integrado, Computo 2012. [En marzo de líneal. Disponible de http://rcmcomputointegrado.blogspot.com.co/2012/03/arquitecturarisc-y-cisc.html [Accedido: 06-jul- 2017]

- "Complex instruction set computing", Wikipedia, 13 de junio de 2011. [En línea]. Disponible en: https://goo.gl/Kd2aN2 [Accedido: 06jul- 20171

- [3] "Reduced instruction set computing", Wikipedia, 7 de abril de 2012. [En línea]. Disponible en: https://goo.gl/j8uLtk [Accedido: 06iul-20171

- "Arquitectura RISC", FAQ-MAC, 17 de marzo de 2012. [En línea]. Disponible en: http: //www.faq - mac.com/2003/10/breve historia - del - risc - por - alejandro - pena/ [Accedido: 06iul-20171

- "Arquitectura ARM", Wikipedia, de abril 2012. [En línea]. Disponible en: https $//es.wikipedia.org/wiki/Arquitectura\_ARM$ [Accedido: 06-jul-2017]

- "Evolución ARM", Wikispaces, familias 17 2012. [En línea]. Disponible en: https//ochobits.wikispaces.com/Evoluci%C3%B3n + defamilias + ARM [Accedido: 06-jul-2017]

- [7] "ARM", Omicrono, 7 de abril de 2012. [En línea]. Disponible en: http: //omicrono.elespanol.com/2012/12/te-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-todo-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explicamos-explisobre-x86-y-arm-diferencias-ventajas-y-paraque - sirve - cada - uno /[Accedido: 06-jul-2017]

- "Supercomputadora", Wikipedia, 2017. [En línea]. Disponible en: https://es.wikipedia.org/wiki/Supercomputadora [Accedido: 06-jul-2017]

- "June 2017", Top 500 The List, 2017. [En línea]. https //www.top500.org/lists/2017/06 [Accedido: 06-jul-2017]

- [10] "Las supercomputadoras Exmás veloces" pansión, 2012. [En línea]. Disponible en: http//expansion.mx/tecnologia/2012/11/13/3- kcomputer japon [Accedido: 06-jul-2017]

[11] "K computer", Wikipedia, 25 de junio de 2017. [En línea]. Disponible

- en: https: //goo.gl/3FLwYc [Accedido: 09-jul-2017]

- "K computer takes first place on HPCG benchmark", Riken, 16 de noviembre de 2016. [En línea]. Disponible en:  $//www.riken.jp/en/pr/topics/2016/20161116\_1/$ http[Accedido: 09-jul-2017]

- [13] "K computer takes first place for the second consecutive time on HPCG benchmark", Riken, 20 de junio de 2017. [En línea]. Disponible en: http://www.riken.jp/en/pr/topics/2017/20170620\_1/ [Accedido: 09-jul-2017]

- [14] H. Miyazaki et al., "Overview of the K computer System". Fujitsu Sci. Tech. J., vol. 48, no. 3, pp.255-264, 2012.

- 6D Mesh-Torus Interconnect 2017. [En línea]. Disponible Fujitsu, httpen: //www.fujitsu.com/downloads/TC/sc10/interconnectof - k - computer.pdf [Accedido: 09-jul-2017]

- [16] Y. Ajima et al., "Tofu: Interconnect for the K computer". Fujitsu Sci. Tech. J., vol. 48, no. 3, pp.280-282, 2012.

- [17] J. Moroo et al., "Operating System for the K Computer". Fujitsu Sci. Tech. J., vol. 48, no. 3, pp.295-297, 2012.

- [18] "Fujitsu Switches Horses for Post-K Supercomputer, Will Ride ARM into Exascale", Top 500 The List, 23 Junio de 2016. [En línea]. Disponible en: https : //www.top500.org/news/fujitsuswitches - horses - for - post - k - supercomputer - will ride - arm - into - exascale / [Accedido: 12-jul-2017]

- [19] "Fujitsu's Next Endeavor: The Post-K Computer", 2016. Fujitsu,[En línea]. Disponible https//www.fujitsu.com/global/Images/fujitsunextendeavor - the - post - k - computer.pdf [Accedido: 12jul-2017]

- [20] "FUJITSU HPC and the Development of the Supercomputer", ARM Developer, 14 de noviembre de 2016. [En línea]. Disponible en: https: //developer.arm.com//media/developer/developers/hpc/files/ARM UG - SC16 - Fujitsu.pdf?la = en [Accedido: 12-jul-2017]

- RIKEN". [21] "ARM-based from and Supercomputer Fujitsu SlideShare, 23 de junio de 2016. [En línea]. Disponible en: https: //www.slideshare.net/PhilHughes14/armbasedsupercomputer - from - fujitsu - and - riken - postk